Bus I2C: assignació, dispositiu, transferència de dades, adreçament

A l'hora de crear un circuit electrònic, molts desenvolupadors s'enfronten a la necessitat d'utilitzar un gran nombre de xips intermedis per combinar, mostrejar i adreçar els seus blocs individuals. Per minimitzar el nombre de xips auxiliars, Philips va proposar una interfície de xarxa sèrie I2C bidireccional de dos cables a la dècada de 1980, dissenyada específicament per gestionar diversos xips dins d'un sol dispositiu.

Actualment, només Philips produeix més d'un centenar de dispositius compatibles amb I2C per a equips electrònics amb una gran varietat de finalitats: memòria, sistemes de processadors de vídeo, convertidors analògic-digital i digital-analògic, controladors de pantalla, etc.

El bus I2C és una modificació del protocol d'intercanvi de dades en sèrie capaç de transmetre dades en sèrie de 8 bits en el mode "ràpid" habitual a velocitats de 100 a 400 kbps. El procés d'intercanvi de dades s'implementa aquí només en dos cables (sense comptar el cable comú): línia SDA per a dades i línia SCL per sincronització.

El bus esdevé bidireccional pel fet que les cascades de sortides dels dispositius connectats al bus tenen col·lectors o canals oberts, replicant així el cablejat AND. Com a resultat, el bus minimitza el nombre de connexions entre xips, deixant menys pins i rastres necessaris a la placa. Com a resultat, el tauler en si resulta ser més senzill, més compacte i tecnològicament més avançat en la producció.

Aquest protocol us permet desactivar els descodificadors d'adreces i altres lògiques de negociació externa. El nombre de xips que poden funcionar simultàniament al bus I2C està limitat per la seva capacitat: un màxim de 400 pF.

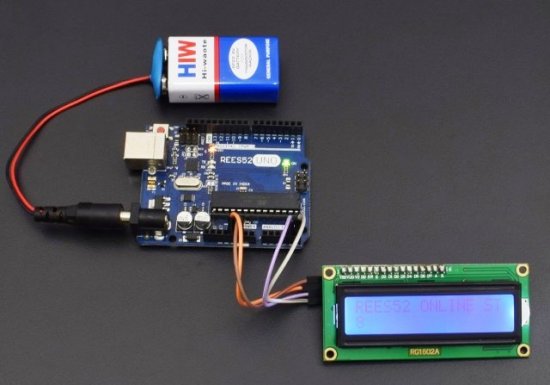

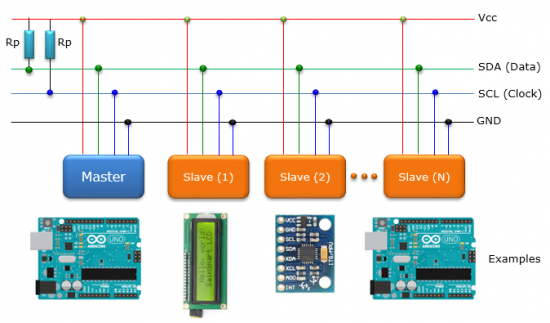

Els circuits integrats compatibles amb I2C tenen un algorisme de supressió de soroll de maquinari per garantir la integritat de les dades fins i tot en presència d'interferències fortes. Aquests dispositius tenen una interfície que permet que els microcircuits es comuniquin entre ells fins i tot quan les seves tensions d'alimentació siguin diferents. A la figura següent, podeu familiaritzar-vos amb el principi de connectar diversos microcircuits mitjançant un bus comú.

Cadascun dels dispositius connectats al bus té la seva pròpia adreça única, aquesta la determina i, d'acord amb la finalitat del dispositiu, pot funcionar com a receptor o com a transmissor. Quan es transmeten dades, aquests dispositius poden ser mestres (mestre) o esclaus (esclaus). El mestre és el dispositiu que inicia la transferència de dades i genera senyals de rellotge a la línia SCL. L'esclau, en relació amb el mestre, és el dispositiu de destinació.

En un moment determinat de funcionament al bus I2C, només un dispositiu pot actuar com a mestre; genera un senyal a la línia SCL.Un mestre pot ser un receptor mestre o un transmissor mestre.

En principi, el bus permet diversos mestres diferents, però imposa restriccions a les característiques de formació de senyals de control i control de l'estat del bus; això vol dir que diversos mestres poden començar a transmetre alhora, però aquests conflictes s'eliminen gràcies a l'arbitratge, és a dir, com es comporta el mestre quan detecta que el bus està ocupat per un altre mestre.

La sincronització d'un parell de dispositius està assegurada pel fet que tots els dispositius estan connectats al bus, formant un cablejat "I". Inicialment, els senyals SDA i SCL són alts.

COMENÇAR i PARAR

L'intercanvi comença amb el mestre generant l'estat «START»: a la línia SDA, el senyal passa d'alt a baix, mentre que la línia SCL té un nivell alt estable. Tots els dispositius connectats al bus perceben aquesta situació com una ordre per iniciar l'intercanvi.

Cada mestre genera un senyal de rellotge individual a la línia SCL quan transmet dades al bus.

L'intercanvi acaba amb la formació de l'estat STOP per part del mestre: a la línia SDA el senyal canvia de baix a alt, mentre que la línia SCL té un nivell alt estable.

El conductor sempre actua com a font dels senyals START i STOP. Tan bon punt s'arregla el senyal «START», vol dir que la línia està ocupada. La línia queda lliure quan es detecta un senyal STOP.

Immediatament després de declarar l'estat START, el mestre canvia la línia SCL baixa i envia el bit més significatiu del primer byte de missatge a la línia SDA. El nombre de bytes d'un missatge no està limitat.Els canvis a la línia SDA només s'activen quan el nivell de senyal a la línia SCL és baix. Les dades són vàlides i no s'han de canviar només quan el pols de sincronització és alt.

El reconeixement que el receptor esclau ha rebut el byte del transmissor mestre es fa configurant un bit de reconeixement especial a la línia SDA després que s'hagi rebut el vuitè bit de dades.

LA CONFIRMACIÓ

Així, l'enviament de 8 bits de dades des del transmissor al receptor acaba amb un pols addicional a la línia SCL quan el dispositiu receptor baixa a la línia SDA, indicant que ha rebut tot el byte.

La confirmació és una part integral del procés de transferència de dades. El mestre genera un pols de sincronització. El transmissor envia un estat baix a SDA mentre el rellotge de reconeixement està actiu. Mentre el pols de sincronització és alt, el receptor ha de mantenir SDA baix.

Si l'esclau de destinació no reconeix la seva adreça, per exemple perquè està ocupat actualment, la línia de dades s'ha de mantenir alta. Aleshores, el mestre pot donar un senyal STOP per avortar l'enviament.

Si la recepció la realitza el receptor mestre, llavors està obligat a informar el transmissor esclau després de la finalització de la transmissió, no confirmant l'últim byte. El transmissor esclau allibera la línia de dades perquè el mestre pugui emetre un senyal d'aturada o un senyal d'inici repetit.

La sincronització dels dispositius està assegurada pel fet que les connexions a la línia SCL es fan segons el principi "AND".

El mestre no té el dret exclusiu de controlar la transició de la línia SCL de baix a alt.Si l'esclau necessita més temps per processar un bit rebut, pot mantenir SCL baix de manera independent fins que estigui preparat per rebre el següent bit de dades. La línia SCL en aquesta situació serà baixa durant la durada del pols de sincronització de baix nivell més llarg.

Els dispositius amb la baixa sostinguda més baixa romandran inactius fins que acabi el període llarg. Quan tots els dispositius hagin acabat el període de sincronització baixa, SCL augmentarà.

Tots els dispositius començaran a marcar un temps alt i el primer dispositiu que completi el seu període serà el primer a establir la línia SCL baixa. Com a resultat, la durada de l'estat baix de SCL estarà determinada per l'estat baix més llarg del pols de sincronització d'un dels dispositius, i la durada de l'estat alt estarà determinada pel període de sincronització més curt d'un dels dispositius. dispositius.

Els senyals de sincronització poden ser utilitzats pels receptors com a mitjà per controlar la transmissió de dades a nivell de bits i bytes.

Si el dispositiu és capaç de rebre bytes a una velocitat alta, però triga una certa quantitat de temps a emmagatzemar el byte rebut o preparar-se per rebre el següent byte, pot continuar mantenint SCL baix després de rebre i reconèixer un byte, forçant el transmissor en estat d'espera.

Un microcontrolador sense circuits de maquinari integrats, per exemple a nivell de bits, pot alentir la velocitat del rellotge augmentant la durada del seu estat baix. Com a resultat, la velocitat en baudis del dispositiu mestre estarà determinada per la velocitat del dispositiu més lent.

DIRECCIÓ

Cada dispositiu connectat al bus I2C té una adreça de programa única a la qual el mestre l'adreça enviant una ordre específica. Els microcircuits del mateix tipus es caracteritzen per un selector d'adreces, implementat en forma d'entrades digitals del selector o en forma analògica. Les adreces es divideixen en l'espai d'adreces dels dispositius connectats al bus.

El mode normal suposa un adreçament de set bits. L'adreçament funciona de la següent manera: després de l'ordre «START», el mestre envia el primer byte, que determina quin dispositiu esclau es necessita per comunicar-se amb el mestre. També hi ha una adreça de trucada comuna que defineix tots els dispositius del bus, tots els dispositius (teòricament) hi responen amb un reconeixement, però a la pràctica això és rar.

Així, els primers set bits del primer byte són l'adreça de l'esclau. El bit menys significatiu, el vuitè, indica la direcció d'enviament de les dades. Si hi ha un «0», la informació s'escriurà del mestre a aquest esclau. Si "1", la informació serà llegida pel mestre d'aquest esclau.

Quan el mestre acaba d'enviar el byte d'adreça, cada esclau compara la seva adreça amb ell. Qualsevol persona amb la mateixa adreça és un esclau i es defineix com a transmissor esclau o receptor esclau, depenent del valor del bit menys significatiu del byte d'adreça.

Una adreça esclau pot incloure parts fixes i programables. Molt sovint un gran nombre de dispositius del mateix tipus funcionen en un sistema, aleshores la part programable de l'adreça permet l'ús d'un màxim del mateix tipus de dispositius al bus. La quantitat de bits del byte d'adreça que es poden programar depèn del nombre de pins lliures del xip.

De vegades, un pin amb una configuració analògica de l'interval d'adreces programables és suficient, per exemple, el SAA1064, un controlador d'indicador LED que té exactament aquesta implementació. El potencial d'un pin determinat determina el desplaçament de l'espai d'adreces del xip de manera que els xips del mateix tipus no entren en conflicte operant al mateix bus. Tots els xips que admeten el bus I2C contenen un conjunt d'adreces que el fabricant especifica a la documentació.

La combinació «11110XX» està reservada per a l'adreçament de 10 bits. Si imaginem l'intercanvi de dades de l'ordre «START» a l'ordre «STOP», quedarà així:

Aquí es permeten formats d'intercanvi de dades simples i combinats. El format combinat fa que entre «START» i «STOP» el mestre i l'esclau puguin actuar com a receptors i transmissors, això és útil per exemple en la gestió de la memòria sèrie.

Deixeu que el primer byte de dades transfereixi una adreça de memòria. Aleshores, repetint l'ordre «START» i llegint l'adreça de l'esclau, les dades de memòria funcionaran. Les decisions per augmentar o disminuir automàticament l'adreça prèviament accedida les pren el desenvolupador del dispositiu després d'haver estudiat prèviament la documentació del xip. D'una manera o altra, després de rebre l'ordre START, tots els dispositius han de restaurar la seva lògica i preparar-se per al fet que l'adreça s'anomenarà ara.