Convertidor analògic a digital: finalitat, classificació i principi de funcionament

Un dispositiu electrònic anomenat convertidor analògic a digital (ADC) s'utilitza per convertir un senyal analògic en un senyal digital (en una seqüència de tipus de codi binari llegible). En el procés de conversió d'un senyal analògic a digital, s'implementen els següents: mostreig, quantificació i codificació.

El mostreig s'entén com la presa de mostres d'un senyal analògic de temps continu de valors individuals (discrets) que cauen en moments de temps associats a determinats intervals i durades de senyals de rellotge que se succeeixen.

La quantificació consisteix a arrodonir el valor d'un senyal analògic seleccionat durant el mostreig al nivell de quantificació més proper, i els nivells de quantificació tenen el seu propi número de seqüència, i aquests nivells es diferencien entre si per un valor delta fix, que no és més que un pas de quantificació.

En sentit estricte, el mostreig és el procés de representar una funció contínua com una sèrie de valors discrets, i la quantificació és la divisió d'un senyal (valors) en nivells. Pel que fa a la codificació, aquí la codificació s'entén com una comparació dels elements obtinguts com a resultat de la quantificació amb una combinació predeterminada de codis.

Hi ha molts mètodes per convertir la tensió en codi. A més, cadascun dels mètodes té característiques individuals: precisió, velocitat, complexitat. Segons el tipus de mètode de conversió, els ADC es classifiquen en tres

-

en paral · lel

-

consistent,

-

sèrie-paral·lel.

Per a cada mètode, el procés de transformació d'un senyal al llarg del temps transcorre a la seva manera, d'aquí el nom. Les diferències rau en com es realitza la quantificació i la codificació: un procediment en sèrie, paral·lel o sèrie-paral·lel per aproximar un resultat digital al senyal convertit.

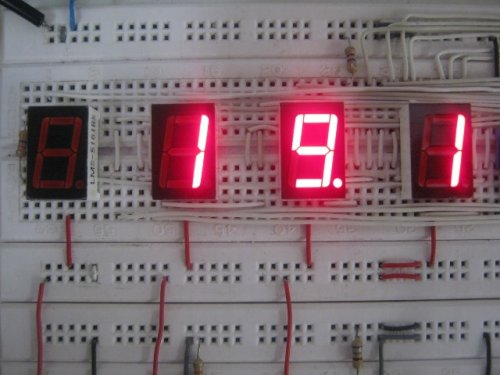

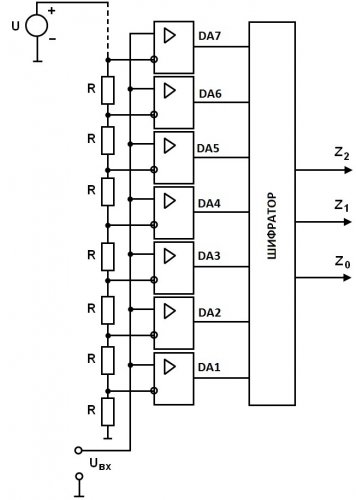

A la figura es mostra el diagrama d'un convertidor analògic-digital paral·lel. Els ADC paral·lels són els convertidors analògic-digital més ràpids.

El nombre de dispositius de comparació electrònica (el nombre total de comparadors DA) correspon a la capacitat de l'ADC: tres comparadors són suficients per a dos bits, set per a tres, 15 per a quatre, etc. El divisor de tensió de la resistència està dissenyat per establir un rang de tensions de referència constants.

La tensió d'entrada (aquí es mesura el valor d'aquesta tensió d'entrada) s'aplica simultàniament a les entrades de tots els comparadors i es compara amb totes les tensions de referència d'aquelles que aquest divisor resistiu permet obtenir.

Aquells comparadors les entrades no inversores dels quals s'alimenten amb una tensió superior a la referència (aplicada pel divisor a l'entrada inversora) donaran una lògica a la sortida, la resta (on la tensió d'entrada és menor que la referència o igual a zero) donarà zero.

Aleshores es connecta un codificador, la seva tasca és convertir una combinació d'uns i zeros en un codi binari estàndard, adequadament entès.

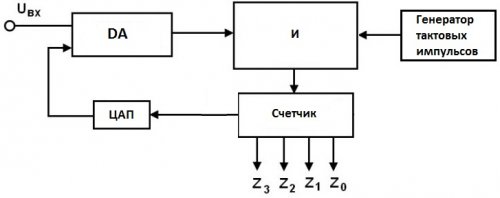

Els circuits ADC per a la conversió en sèrie són menys ràpids que els circuits convertidors en paral·lel, però tenen un disseny elemental més senzill. Utilitza un comparador, lògica AND, un rellotge, un comptador i un convertidor digital-analògic.

La figura mostra un diagrama d'aquest ADC. Per exemple, mentre que la tensió mesurada aplicada a l'entrada del circuit comparador és superior al senyal de rampa de la segona entrada (referència), el comptador compta els polsos del generador de rellotge. Resulta que la tensió mesurada és proporcional al nombre de polsos comptats.

També hi ha ADC en sèrie-paral·lel, on el procés de conversió d'un senyal analògic a un senyal digital es separa a l'espai, de manera que resulta que la velocitat màxima de compensació s'aconsegueix amb una complexitat mínima.