Dispositius digitals: xancletes, comparadors i registres

Els dispositius digitals estan construïts sobre elements lògics, per tant obeeixen les lleis de l'àlgebra lògica. Els dispositius bàsics de la tecnologia digital, juntament amb els dispositius lògics, són les xancletes.

Els dispositius digitals estan construïts sobre elements lògics, per tant obeeixen les lleis de l'àlgebra lògica. Els dispositius bàsics de la tecnologia digital, juntament amb els dispositius lògics, són les xancletes.

Trigger (disparador anglès - trigger) - un dispositiu electrònic que té dos estats estables i pot saltar d'un estat a un altre sota la influència d'un impuls extern.

Els disparadors o, més precisament, els sistemes de disparador s'anomenen una gran classe de dispositius electrònics que tenen la capacitat de romandre en un dels dos estats estables durant molt de temps i alternar-los sota la influència de senyals externs. Cada condició d'activació es reconeix fàcilment pel valor de la tensió de sortida.

Cada estat d'activació correspon a un cert nivell de tensió de sortida (alt o baix):

1) el disparador està configurat en un estat: nivell «1».

2) el flip-flop es reinicia - nivell «0» a la sortida.

L'estat estacionari es manté tant com es desitgi i es pot canviar mitjançant un pols extern o desconnectant la tensió d'alimentació. Che.un flip-flop és un element de memòria elemental capaç d'emmagatzemar la unitat d'informació més petita (un bit) «0» o «1».

Els flip-flops es poden construir sobre elements discrets, elements lògics, en un circuit integrat o formen part d'un circuit integrat.

Els principals tipus de xancletes són: RS-, D-, T- i JK-flippers... A més, les xancletes es divideixen en asíncrones i síncrones. En l'accionament asíncron, el canvi d'un estat a un altre es fa directament amb l'arribada d'un senyal a l'entrada d'informació. A més de les entrades de dades, els flip-flops sincronitzats tenen una entrada de rellotge. La seva commutació només es produeix en presència d'un pols de rellotge d'habilitació.

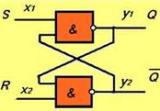

Un disparador RS té almenys dues entrades: S (set — set) — el disparador està configurat a l'estat del nivell «1» i R (reset) — el disparador es reinicia al nivell «0». (Fig. 1).

En presència de l'entrada C, el flip-flop és sincrònic: la commutació del flip-flop (canvi d'estat de la sortida) només es pot produir en el moment de l'arribada del pols de sincronització (sincronització) a l'entrada C.

Figura 1 — Representació gràfica convencional del flip-flop RS i el propòsit de les conclusions a) asíncron, b) síncron

A més de la sortida directa, el flip-flop també pot tenir una sortida inversa, el senyal de la qual serà oposat.

La taula 1 mostra els estats que pot assumir el flip-flop durant el funcionament. La taula mostra els valors dels senyals d'entrada S i R en un determinat instant de temps tn i l'estat del flip-flop (de la sortida directa) en el següent instant de temps tn + 1 després de l'arribada del següent llegums. El nou estat de disparador també es veu afectat per l'estat anterior de Q n.

Che.si cal escriure al disparador «1» — donem un pols a l'entrada S, si «0» — enviem un pols a l'entrada R.

La combinació S = 1, R = 1 és una combinació prohibida perquè és impossible predir quin estat s'establirà a la sortida.

Taula 1 - Taula d'estats de flip-flop RS síncron

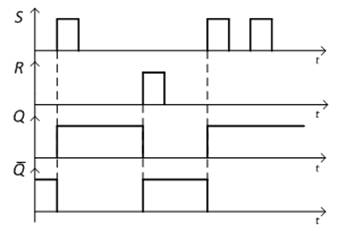

El funcionament del flip-flop també es pot veure mitjançant diagrames de temps (Fig. 2).

Figura 2 — Diagrames de temps d'un flip-flop RS asíncron

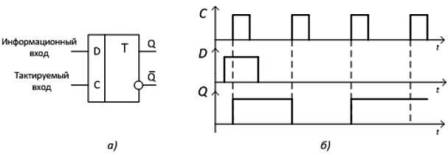

D-trigger (de l'anglès delay — delay) té una entrada d'informació i una entrada de rellotge (sincronització) (Fig. 3).

El flip-flop D emmagatzema i emmagatzema a la sortida Q el senyal que hi havia a l'entrada de dades D en el moment de l'arribada del pols de rellotge C. el flip-flop emmagatzema informació escrita quan C = 1.

Taula 2-Taula d'estats del flip-flop D

Figura 3 — D -disparador: a) representació gràfica convencional, b) diagrames de temps de funcionament

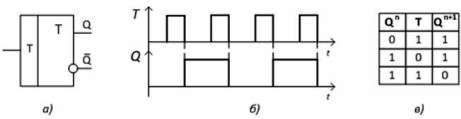

Els activadors T (de l'anglès tumble — overturning, somersault), també anomenats xancletes de recompte, tenen una entrada d'informació T. Cada pols (decaiment del pols) de l'entrada T (entrada de comptatge) canvia el disparador a l'estat contrari.

La figura 4 mostra la simbologia del disparador T (a) i els diagrames de temps de l'operació (b).

Figura 4-T-flip-flop a) notació gràfica convencional, b) diagrames de temps de l'operació c) taula d'estats

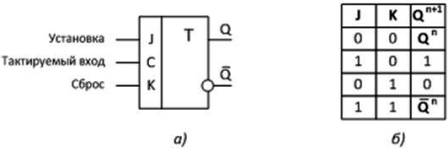

Un disparador JK (de l'anglès jump — jump, keer — hold) té dues entrades de dades J i K i una entrada de rellotge C. L'assignació dels pins J i K és similar a l'assignació dels pins R i S, però el disparador té no hi ha combinacions prohibides. Si J = K = 1, canvia el seu estat al contrari (Fig. 5).

Amb la connexió adequada de les entrades, el disparador pot realitzar les funcions dels disparadors RS-, D-, T, és a dir. és un desencadenant universal.

Figura 5 -JK -flip-flop a) notació gràfica convencional, b) taula d'estats abreujada

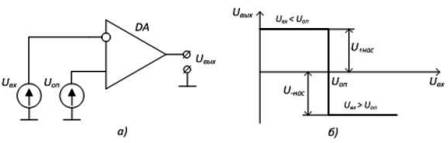

Comparador (comparar — comparar) — un dispositiu que compara dos voltatges — entrada Uin amb una referència Uref. La tensió de referència és una tensió constant amb polaritat positiva o negativa, la tensió d'entrada canvia amb el temps. El circuit comparador més senzill basat en un amplificador operacional es mostra a la figura 6, a. Si Uin Uop a la sortida U — us (Fig. 6, b).

Figura 6 — Comparador d'amplificadors operacionals: a) l'esquema més senzill b) característiques de rendiment

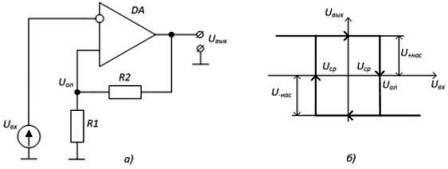

Un comparador de retroalimentació positiva s'anomena disparador de Schmitt. Si el comparador canvia d'«1» a «0» i viceversa a la mateixa tensió, el disparador Schmitt - a diferents voltatges. La tensió de referència crea un circuit PIC R1R2, el senyal d'entrada s'alimenta a l'entrada inversora de l'amplificador operatiu. La figura 7, b, mostra la característica de transferència del disparador de Schmitt.

A una tensió negativa a l'entrada d'inventari del SO Uout = U + sat. Això vol dir que una tensió positiva actua sobre l'entrada no inversora. A mesura que augmenta la tensió d'entrada, el corrent Uin > Uneinv. (Uav — disparador) el comparador passa a l'estat Uout = U -sat. S'aplica una tensió negativa a l'entrada no inversora. En conseqüència, amb una disminució de la tensió d'entrada en el moment Uin <Uneinv. (Uav — disparador) el comparador entra a l'estat Uout = U + sat.

Figura 7 — Funcionament de Schmitt d'un amplificador operacional: a) l'esquema més simple b) característiques de rendiment

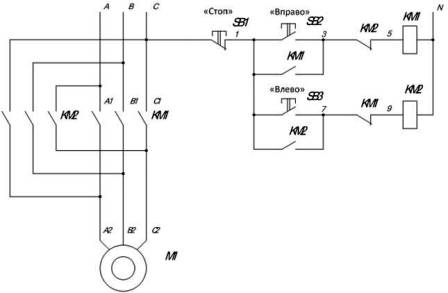

Un exemple. La figura 8 mostra un esquema d'un relé-contactor per controlar un motor elèctric, permetent-lo arrencar, aturar-lo i fer marxa enrere.

Figura 8 — Esquema de control del motor relé-contactor

La commutació del motor elèctric es realitza mitjançant arrancadors magnètics KM1, KM2. Els contactes tancats lliurement KM1, KM2 impedeixen el funcionament simultani dels arrencadors magnètics. Els contactes oberts lliurement KM1, KM2 proporcionen l'autobloqueig dels botons SB2 i SB3.

Per millorar la fiabilitat del funcionament, cal substituir els circuits de control de relé-contactor i els circuits de potència per un sistema sense contacte que utilitzi dispositius i dispositius semiconductors.

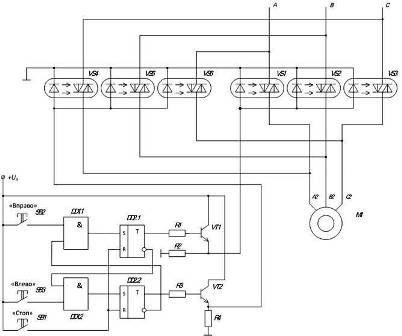

La figura 9 mostra un circuit de control de motor sense contacte.

Els contactes de potència dels arrencadors magnètics es van substituir per opto-simistors: KM1-VS1-VS3, KM2-VS4-VS6. L'ús d'optosimistors permet aïllar un circuit de control de baixa intensitat d'un circuit d'alimentació potent.

Els disparadors proporcionen botons autoblocants SB2, SB3. Elements lògics I asseguren l'activació simultània només d'un dels arrencadors magnètics.

Quan s'obre el transistor VT1, el corrent flueix a través dels LED del primer grup d'opto-simistors VS1-VS3, assegurant així el flux de corrent a través dels bobinatges del motor.L'obertura del transistor VT2 subministra el segon grup d'opto-simistors VS4 -VS6, assegurant la rotació del motor elèctric en l'altre sentit.

Figura 9 — Circuit de control del motor sense contacte

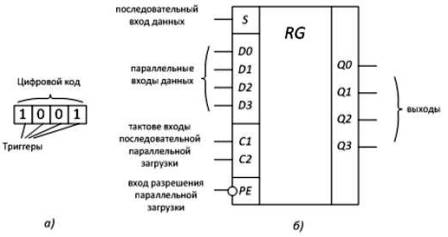

Registre: un dispositiu electrònic dissenyat per a l'emmagatzematge i la conversió a curt termini de nombres binaris de diversos dígits. El registre consta de xancletes, el nombre de les quals determina quants bits d'un nombre binari pot emmagatzemar el registre, la mida del registre (Fig. 10, a). Els elements lògics es poden utilitzar per organitzar el funcionament dels disparadors.

Figura 10 — Registre: a) representació general, b) notació gràfica convencional

Segons el mètode d'entrada i sortida de la informació, els registres es divideixen en paral·lel i en sèrie.

En un registre seqüencial, els flip-flops es connecten en sèrie, és a dir, les sortides del flip-flop anterior passen informació a les entrades del següent flip-flop. Les entrades C del rellotge del flip-flop estan connectades en paral·lel. Aquest registre té una entrada de dades i una entrada de control: entrada de rellotge C.

Un registre paral·lel escriu simultàniament a xancles per als quals hi ha quatre entrades de dades.

La figura 10 mostra l'UGO i l'assignació de pins d'un registre en sèrie paral·lel de quatre bits.